Journal of Engineering Research and Reports

16(4): 1-7, 2020; Article no.JERR.60632 ISSN: 2582-2926

# Addressing Package Voids on Extremely Small Leadframe Device

A. Sumagpang Jr.<sup>1\*</sup> and F. R. Gomez<sup>1</sup>

<sup>1</sup>New Product Development and Introduction, STMicroelectronics, Inc., Calamba City, Laguna, 4027, Philippines.

Authors' contributions

This work was carried out in collaboration between both authors. Both authors read, reviewed and approved the final manuscript.

## Article Information

DOI: 10.9734/JERR/2020/v16i417172 <u>Editor(s):</u> (1) Dr. Y. Thiagarajan, Sri Venkateshwaraa College of Engineering and Technology, India. <u>Reviewers:</u> (1) J. Barsana Banu, Mahath Amma Institute of Engineering and Technology, India. (2) Atishey Mittal, SRM Institute of Science and Technology, India. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/60632</u>

**Original Research Article**

Received 18 June 2020 Accepted 23 August 2020 Published 01 September 2020

# ABSTRACT

The paper focused in addressing the package voids defect of a semiconductor device utilizing an extremely small leadframe technology. Potential risk analysis and pareto diagram were completed to identify the top reject contributors and eventually come-up with the robust solution. A comprehensive design of experiments (DOE) was completed and solution validation was performed to formulate the effective corrective actions. Results revealed that package voids were addressed by optimizing the molding process focusing on the molding temperature and curing time. A significant improvement of 95 % for package voids reduction was achieved. For future works, the parameters and learnings could be used on devices with similar configuration.

Keywords: Compression molding; leadframe; line-stressing; package voids; semiconductor.

# **1. INTRODUCTION**

New trends and continuous development in semiconductor technology offer great challenges in assembly manufacturing industry. An imperative challenge for any industry is to maintain its competitive market position and value. Important to note that failure to provide customer expectation in terms of quality and time-to-market would result to possible business failure. This critical situation should really be prevented that is why a line-stressing is being employed in preparation to mass or fullproduction mode.

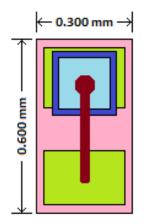

The device in focus is a newly-introduced leadframe package in the plant having an extremely small footprint as illustrated in Fig. 1. The device functions as a diode with a single wire connection, for mobile phones and computer applications. Regardless of its simple geometry, it is considered as a critical device as state-of-the-art platforms are needed to meet its output process.

Fig. 1. Device dimension

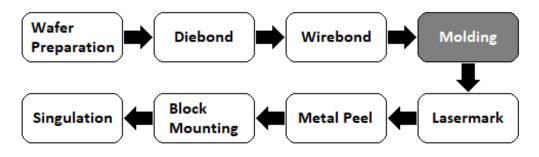

The device has a very thin die and with extremely small total package dimension. The assembly manufacturing process includes a step-cutting method of wafers, compression molding, and in-strip testing, that are not commonly used in other semiconductor industries. A part of the assembly process flow is shown in Fig. 2. Worthy to note that assembly and test process flow varies with the product and the technology [1-4]. With the continuing technology development and state-of-the-art

platforms, challenges in semiconductor industry are inevitable [5-8].

Assembly defects were encountered during the line-stressing and ramp-up of the device. Critical processes were identified using risk analysis, and one of which focused on the molding process as identified in Table 1. Evaluation was completed before the risk build to accelerate confidence on line-stressing. Moreover, potential risk analysis was given contingency plans and established corrective actions.

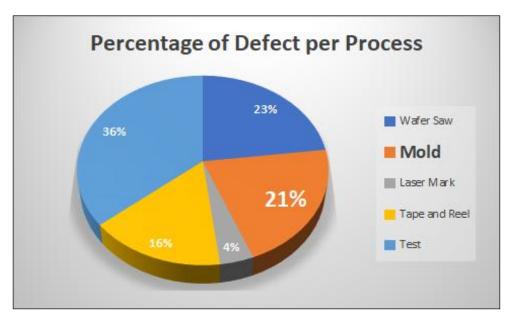

Reject contributors on the identified critical processes are shown in Fig. 3 chart. Molding is one critical process identified with output abnormalities as a result of unoptimized parameters which are typically attributed to newly-introduced devices.

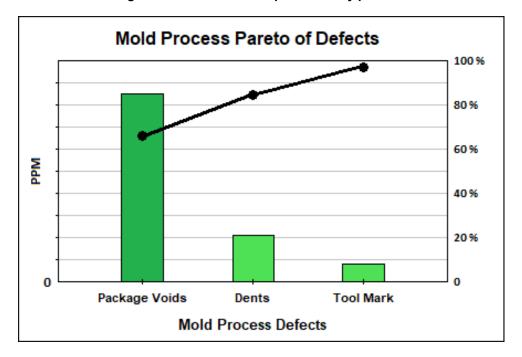

Of the 21 % defect contribution of the molding process, pareto diagram in Fig. 4 shows package voids or mold voids as the top reject parts per million (ppm) contributor. Parameter optimization is one of the factors to be checked as the device has no other similar product in the plant for reference. Benchmarking from other semiconductor plants is being considered to have a reference or baseline for critical process parameters.

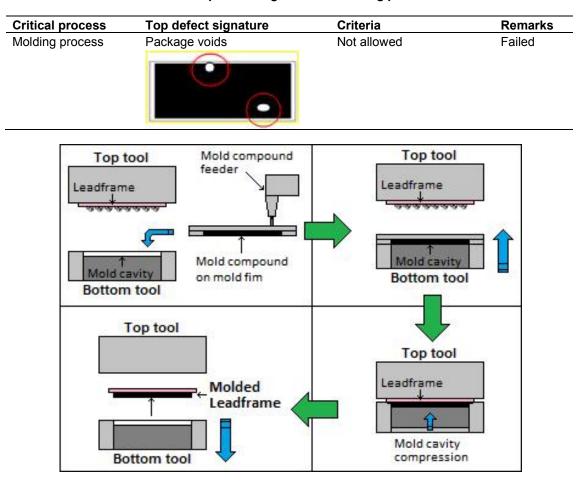

Тор rejects based on pareto diagram substantially affect the yield and delivery during line-stressing performance. With this, process optimization is highly recommended at linestressing before it reaches the full-production mode. Table 2 shares the top defect signature of the molding process. Further investigation and analysis of failures were done by collecting the actual reject samples at this critical process. This eventually is essential in developing the corrective actions and improvement.

Fig. 2. Assembly process flow

Sumagpang Jr. and Gomez; JERR, 16(4): 1-7, 2020; Article no.JERR.60632

| Identified risk                                                               | Resulting                                       | Evaluation before action |        |       | Identified action                                     |

|-------------------------------------------------------------------------------|-------------------------------------------------|--------------------------|--------|-------|-------------------------------------------------------|

|                                                                               | potential risk                                  | Probability              | Impact | Class |                                                       |

| 0.3 mm package molding,<br>package molding defects,<br>voids, incomplete fill | <ul><li>Low yield</li><li>Reliability</li></ul> | 9                        | 9      | A     | Capability using<br>compression<br>molding technology |

Table 1. Potential risk analysis at molding process

Fig. 3. Defect contribution per assembly process

Fig. 4. Pareto diagram of mold process rejects with package voids as top contributor

## 2. LITERATURE REVIEW

One of the fundamental components in the production of semiconductor devices is the molding compound, which is a packaging material for encapsulation to protect the device from external environment [9]. The device uses compression molding as illustrated in Fig. 5.

The advantages of compression molding system are zero to less wire damage, good filling on narrow gap on die, and no cull or runner. The technology was necessary for the device due to the constraint of narrow mold cap thickness. With this, the device is susceptible to voids during molding, thus package voids became the top reject contributor. Package voids are usually easy to address, but this would require a comprehensive parameter optimization through design of experiments (DOE). Ultimately, DOE was done to achieve the desired parameter range for molding process considering the critical input and output responses, with the package voids as the primary output response.

## 3. METHODOLOGY

DOE evaluation for compression molding was conducted with the intent to determine and define window for critical parameter range that would eliminate package voids. Shown in Table 3 is the DOE evaluation matrix prepared using a statistical software that automatically provides the combination of runs.

#### Table 2. Top defect signature of molding process

Fig. 5. Compression molding mechanism

| Run | Pattern | Mold temperature (°C) | Cure time (s) | Package voids         |

|-----|---------|-----------------------|---------------|-----------------------|

| 1   | 1-1     | 170                   | 160           | Output response to be |

| 2   | 1-2     | 170                   | 180           | measured              |

| 3   | 1-3     | 170                   | 200           |                       |

| 4   | 2-1     | 175                   | 160           |                       |

| 5   | 2-2     | 175                   | 180           |                       |

| 6   | 2-3     | 175                   | 200           |                       |

| 7   | 3-1     | 180                   | 160           |                       |

| 8   | 3-2     | 180                   | 180           |                       |

| 9   | 3-3     | 180                   | 200           |                       |

Table 3. DOE evaluation matrix

Full-factorial design with a total of nine runs was created. Using the statistical software tool, mold temperature and cure time were identified as the most critical parameters that affect package voids occurrence. Results are discussed in the succeeding section.

## 4. RESULTS AND ANALYSIS

During development, the initial problem encountered was package voids in every shot. Together with the mold machine field support and the mold compound technical support, DOE was performed using a matrix of different batches of mold compound and sets of mold parameters, as shared in Fig. 6.

DOE results of compression molding showed that optimum parameters in terms of package

voids can be achieved by using the 175°C and 180 seconds curing time regardless of molding compound used.

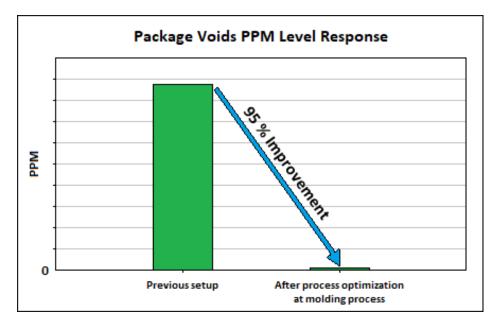

After the implementation of the identified solutions and corrective actions, level of rejections was monitored. Fig. 7 depicts the improvement in the ppm level. Actual ppm values are intentionally not shown due to confidentiality.

An improvement of 95 % for die chippings reduction was achieved through the comprehensive DOE. Assembly yield trend stabilized after the implementation, optimization, and sustainability of the improvement and all corrective actions. Importantly, this indicates manufacturing preparedness for full-production mode.

| Molding Type<br>Mold Compound |           | Transfer<br>Mold | Compression Mold     |      |      |      |      |                       |

|-------------------------------|-----------|------------------|----------------------|------|------|------|------|-----------------------|

|                               |           | TM1              | CM1                  | CM2  | CM3  | CM4  |      |                       |

| Powder sieving N              |           | No               | 150um on<br>1mm pass |      |      |      |      |                       |

| Spiral flow inch              |           | inch             | 33                   | 55   | 55   | 50   | 53   | 1                     |

| Flash le                      |           | mm               | 1,1                  | 1.7  | 1.7  | 1.7  | 1.4  |                       |

| Hot hardness(90sec)           |           |                  | 88                   | 72   | 72   | 63   | 55   | Need longer cure time |

| Gelation time(175C)           |           | 540              | 32                   | 75   | 90   | 102  | Q3   | such as 175°C/180s    |

| Viscosil                      | y(175C)   | poise            | 230                  | 140  | 140  | 250  | 270  |                       |

| Disk flo                      |           | mm               | 78                   | 94   | 94   | 91   | 91   | 1                     |

| Tg                            | 805       | degC             | 135                  | 135  | 135  | 130  | 125  | 1                     |

| CTE                           | alpha-1   | ppm/C            | 8                    | 7    | 7    | 8    | 7    | 1                     |

|                               | alpha-2   | ppm/C            | 30                   | 27   | 27   | 30   | 27   | 1                     |

| Flexura                       | Modulus   | kgtmm2           | 2400                 | 2400 | 2400 | 2500 | 2500 | 1                     |

| Flexura                       | Strength  | kg0mm2           | 15                   | 14   | 15   | 15   | 15   | 1                     |

|                               | bsorption | 5                | 0.23                 | 0.23 | 0.23 | 0.27 | 0.28 | 1                     |

| Mold sh                       | vinkage   | - %              | 0.06                 | 0.05 | 0.06 | 0.05 | 0.11 | 1                     |

Fig. 6. DOE matrix for compression molding process optimization

Fig. 7. Improvement after optimization and implementation of corrective actions

## 5. CONCLUSION AND RECOMMENDA-TIONS

Comprehensive engineering analyses with the aid of statistical analysis were done in solving and addressing the package voids of an extremely small device at molding process. Through DOE, parameters optimization was formulated, with package voids occurrence significantly minimized by achieving the optimum molding temperature and curing time. A 95 % improvement for package voids reduction was ultimately achieved.

Process optimization plays an essential role to as early as line-stressing stage, before fullproduction release can be granted. It is imperative that when newly-introduced devices are coming in, critical processes should be identified and that appropriate improvement, corrective actions, and solutions be made so that when full-production is set, both quality and speed could be achieved. Techniques and learnings shared in this paper could be used for future works on semiconductor devices with comparable configuration. Also, studies and works discussed in [10-12] are helpful in improving the assembly processes particularly in the yield improvement.

# ACKNOWLEDGEMENTS

The authors would like to express sincerest gratitude to the Management Team and the New

Product Development & Introduction (NPD-I) team for the positive support.

# **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

## REFERENCES

- May GS, Spanos CJ. Fundamentals of semiconductor manufacturing and process control. 1<sup>st</sup> Ed., Wiley-IEEE Press, USA; 2006.

- 2. Nenni D, McLellan P. Fabless: the transformation of the semiconductor industry. Create Space Independent Publishing Platform, USA; 2014.

- Harper C. Electronic packaging and interconnection handbook. 4<sup>th</sup> Ed., McGraw-Hill Education, USA; 2004.

- Geng H. Semiconductor manufacturing handbook. 2<sup>nd</sup> Ed., McGraw-Hill Education, USA; 2017.

- Tsukada Y, Kobayashi K, Nishimura H. Trend of semiconductor packaging, high density and low cost. Proceedings of the 4th International Symposium on Electronic Materials and Packaging. Taiwan. 2002;1-6.

- Yeap LL. Meeting the assembly challenges in new semiconductor packaging trend. 34<sup>th</sup> IEEE/CPMT International Electronic

Manufacturing Technology Symposium (IEMT). Malaysia. 2010;1-5.

- Liu Y, Irving S, Luk T, Kinzer D. Trends of power electronic packaging and modeling. 10th Electronics Packaging Technology Conference. Singapore. 2008;1-11.

- Saha S. Emerging business trends in the semiconductor industry. Proceedings of PICMET '13: Technology Management in the IT-Driven Services (PICMET). USA. 2013;2744-2748.

- Ardebili H, Zhang J, Pecht M. Encapsulation technologies for electronic applications. 2<sup>nd</sup> Ed., William Andrew Applied Science Publishers, Elsevier, USA; 2018.

- Sumagpang Jr. A, Gomez FR, Rodriguez R. Tool setup improvement for package scratch mitigation at end-of-line process. Journal of Engineering Research and Reports. 2020;12(3):1-5.

- Gomez FR, Mangaoang Jr. T. Elimination of esd events and optimizing waterjet deflash process for reduction of leakage current failures on qfn-mr leadframe devices. Journal of Electrical Engineering, David Publishing Co. 2018;6(4):238-243.

- Pulido J, Gomez FR, Graycochea Jr. E. Lead scratch resolution through wirebonding process optimization on qfn packages. Journal of Engineering Research and Reports. 2020;15(1):29-33.

© 2020 Sumagpang Jr. and Gomez; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

> Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/60632